### WBC3526DB26UJ0

### Bottom port digital silicon Microphone

#### **Descriptions**

WBC3526DB26UJ0is a Silicon Microphone with digital output and bottom inlet for sound input. It consists of a MEMS sensor and an encoder IC. It converts sensor analog output signal into 1-bit digital PDM data. The digital output format eliminates AC coupling capacitor, reduces RF noise coupling and eases PCB layout requirement.

WBC3526DB26UJ0 is a cost-effective alternative to traditional electret condenser microphone (ECM). Provided on tap-and-reel, it is ideally suited for high volume applications. And it can be processed directly to customer's PCB using standard automatic pick-and-place equipment and surface mounted via standard solder reflow equipment.

WBC3526DB26UJ0 can be used to implement the array microphones. Speech quality can be significantly improved by combining two microphones.

The WBC3526DB26UJ0is manufactured in a compact 3.50mm\*2.65mm\*0.98mm, 5-pin package.

### Features

- PDM Output High SNR

- Multiple performance modes

- Ultra-Stable Performance

- Standard SMD Reflow

- RoHS/Halogen free compliant

- Omnidirectional

### Applications

- Smart phones Smart speakers

- Portable communication device

- Notebook and desktop

- Digital still cameras

- Portable music recorders

**Product appearance**

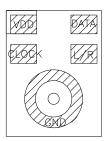

#### Pin configuration (Bottom view)

Marking (Top view)

Y = Year code WW = Week code X X = Data code

#### Order information

| Device              | Package(mm)    | Shipping       |

|---------------------|----------------|----------------|

| WBC3526DB26UJ0-5/TR | 3.50*2.65*0.98 | 5000/Reel&Tape |

## **Absolute Maximum Ratings**

| Parameter                   | Maximum Ratings | Unit |

|-----------------------------|-----------------|------|

| Power supply voltage        | 6.5             | V    |

| Operation temperature range | -40~85          | °C   |

| Storage temperature range   | -40~125         | °C   |

Stresses at the maximum ratings shown in Table 1 may cause permanent damage to the device. These are stress ratings only at which the device may not function when an operation at these or any other condition beyond those specified under "Electro-Acoustic Specifications".

## **Acoustic & Electrical Specifications**

### **Normal Mode Electrical Specifications**

Test condition: +25±2°C, 60% $\sim$ 70% RH, 86~106Kpa, F<sub>CLK</sub>=2.4MHz, V<sub>DD</sub>=1.8V, no load, unless otherwise noted.

| Symbol | Description                              | Min. | Тур. | Max. | Units             |

|--------|------------------------------------------|------|------|------|-------------------|

| Fclk   | Clock Frequency                          | 1.3  | 2.4  | 4.8  | MHz               |

| lod    | Supply Current <sup>1</sup>              |      | 770  | 900  | uA                |

| S      | Sensitivity <sup>3</sup> , 94dB SPL@1KHz | -27  | -26  | -25  | dBFS <sup>2</sup> |

| ΔS     | Sensitivity drop                         | <0.5 |      |      | dBFS              |

|        | 20-5KHz Bandwidth, A-Weighted            |      | 68   |      | dB(A)             |

| SNR    | 20-8KHz Bandwidth, A-Weighted            |      | 66.5 |      | dB(A)             |

|        | 20-20KHz Bandwidth, A-weighted           | 63   | 65   |      | dB(A)             |

|        | 94dB SPL@1KHz                            |      | 0.15 | 0.5  | %                 |

| THD    | 118dB SPL@1KHz                           |      | 1    |      | %                 |

| AOP    | 10%THD@1KHz                              |      | 121  |      | dBSPL             |

| PSR    | Measured with 217Hz,100mVpp square wave  |      | -90  | -80  | dBFS              |

| PSRR   | Measured with 1KHz,200mVpp sinewave      |      | 60   |      | dBFS              |

### Low Power Mode Electrical Specifications

Test condition: +25±2°C, 60% $\sim$ 70% RH, 86~106Kpa, F<sub>CLK</sub>=768KHz, V<sub>DD</sub>=1.8V, no load, unless otherwise noted.

| Symbol          | Description                                        | Min. | Тур. | Max. | Units |

|-----------------|----------------------------------------------------|------|------|------|-------|

| Fclk            | Clock Frequency                                    | 150  | 768  | 900  | KHz   |

| I <sub>DD</sub> | Supply Current                                     |      | 340  | 450  | uA    |

| S               | Sensitivity, 94dB SPL@1KHz                         | -27  | -26  | -25  | dBFS  |

| ΔS              | Sensitivity drop                                   | <0.5 |      | dBFS |       |

| SNR             | 20Hz~8KHz Bandwidth, A-weighted                    |      | 64   |      | dB(A) |

|                 | 94dB SPL@1KHz                                      |      | 0.15 | 0.5  | %     |

| THD             | 118dB SPL@1KHz                                     |      | 1    |      | %     |

| AOP 10%THD@1KHz |                                                    |      | 120  |      | dBSPL |

| PSR             | Measured with 217Hz, 100mV $_{\rm pp}$ square wave |      | -90  | -80  | dBFS  |

| PSRR            | Measured with 1KHz,200mVpp sinewave                |      | 60   |      | dBFS  |

Note 1: The current consumption depends on the applied clock frequency and the load on the DATA

output

- Note 2: dBFS=20\*logA/B, where A is the level of signal, and B is the level that corresponds to full-scale level

- Note 3: Relative to the rms level of a sine wave with positive amplitude equal to100%1s density and Negative amplitude equal to 0% 1s density

- Note 4: Frequency response, sensitivity and current consumption are tested by 100% on product line.

### **General Electrical Specifications**

Test condition: +25±2°C, 60%~70% RH, 86~106Kpa, no load, unless otherwise noted.

| Symbol           | Description                                                                                           | Description                                                  |     | Тур.                      | Max. | Units |  |

|------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----|---------------------------|------|-------|--|

| Vdd              | Supply Voltage                                                                                        | Supply Voltage                                               |     | 1.8                       | 3.6  | V     |  |

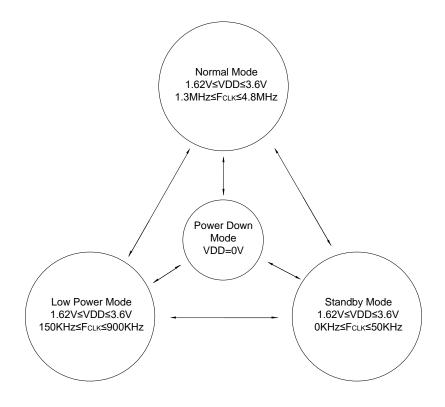

| ISLEEP           | Power Consumption<br>FCLK<50KHzor CLK (                                                               |                                                              |     | 6                         | 50   | uA    |  |

|                  |                                                                                                       | Standby Mode                                                 |     |                           | 50   | KHz   |  |

| Fclk             | Clock Frequency                                                                                       | Low Power Mode                                               | 150 | 768                       | 900  | KHz   |  |

|                  |                                                                                                       | Normal Mode                                                  | 1.3 | 2.4                       | 4.8  | MHz   |  |

| Data Format      |                                                                                                       |                                                              |     | 1/2 Cycle PDM             |      |       |  |

| Directivity      |                                                                                                       |                                                              |     | lirectional               |      |       |  |

| Polarity         | Increasing sound pre-                                                                                 | Increasing sound pressure                                    |     | Increasing density of 1's |      |       |  |

| Isc              | Short circuit current,                                                                                | Short circuit current, Grounded DATA                         |     |                           | 20   | mA    |  |

| CLOAD            | Load capacitance                                                                                      | Load capacitance                                             |     |                           | 100  | pF    |  |

| Reset time       | Time to start up in any mode after VDD has<br>been off for more than 10ms, while CLOCK<br>remained on |                                                              |     |                           | 20   | ms    |  |

| Start-up time    | Start-up into normal r                                                                                | Start-up into normal mode or LP mode                         |     |                           | 20   | ms    |  |

| Mode-switch time |                                                                                                       | Mode-switch Normal mode to LP mode or LP mode to Normal mode |     |                           | 20   | ms    |  |

# **Microphone State Diagram**

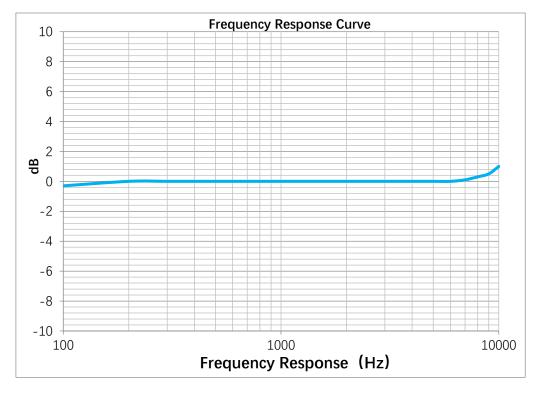

## **Frequency Response Curve**

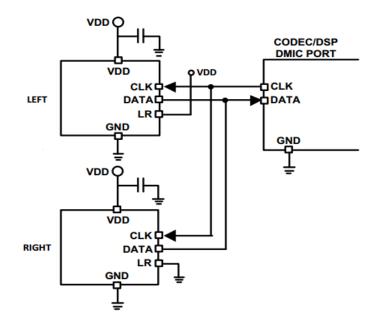

# **Application Information**

| Microphone | SELECT | Asserts DATA On    | Latch DATA On      |

|------------|--------|--------------------|--------------------|

| Mic (High) | Vdd    | Rising Clock Edge  | Falling Clock Edge |

| Mic (Low)  | GND    | Falling Clock Edge | Rising Clock Edge  |

Note:

- All GND pins must be connected to ground.

- Capacitors near the microphone should not contain Class 2 dielectrics.

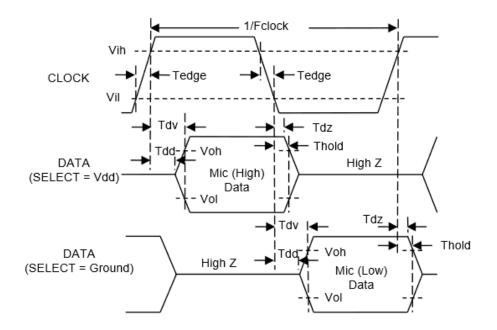

## **Clock Timing Diagram**

# **Timing Characteristics**

| Parameter                  | Symbol          | Min.                  | Тур. | Max.                 | Unit | Note                                                                                                  |

|----------------------------|-----------------|-----------------------|------|----------------------|------|-------------------------------------------------------------------------------------------------------|

| Clock duty cycle           |                 | 40                    | 50   | 60                   | %    |                                                                                                       |

| Operation Voltage          | V <sub>DD</sub> | 1.62                  |      | 3.6                  | V    |                                                                                                       |

| Input Logic Low Level      | VIL             | -0.3                  |      | 0.35×V <sub>DD</sub> | V    |                                                                                                       |

| Input Logic High Level     | VIH             | 0.65×V <sub>DD</sub>  |      | V <sub>DD</sub> +0.3 | V    |                                                                                                       |

| Output Logic Low Level     | Vol             |                       |      | 0.45                 | V    |                                                                                                       |

| Output Logic High Level    | Vон             | V <sub>DD</sub> -0.45 |      |                      | V    |                                                                                                       |

| Clock rise time            | t <sub>CR</sub> |                       |      | 6                    | ns   | 35%~65%                                                                                               |

| Clock fall time            | tcF             |                       |      | 6                    | ns   | 65%~35%                                                                                               |

| Delay time for data valid  | t <sub>DV</sub> | 40                    |      | 100                  | ns   | Delay time from clock<br>edge(0.50 x VDD) to data<br>valid( <v<sub>OL or &gt; V<sub>OH</sub>)</v<sub> |

| Delay time for data driven | tod             | 25                    |      | 50                   | ns   | Delay time from clock<br>edge (50% VDD) to data<br>driven.                                            |

| Delay time for data high Z | t <sub>Hz</sub> | 5                     |      | 20                   | ns   | Delay time from clock<br>edge(50% VDD) to data                                                        |

## WBC3526DB26UJ0

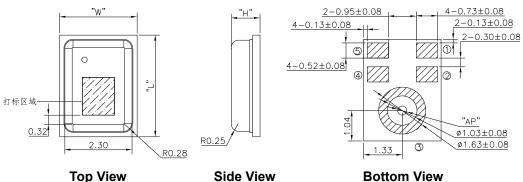

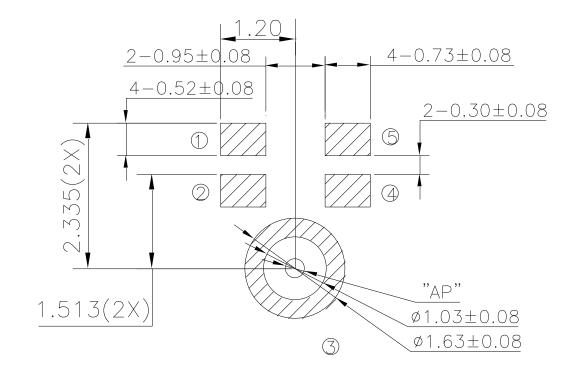

## **Mechanical Specifications**

**Top View**

**Bottom View**

| ltem               | Dimension | Tolerance |

|--------------------|-----------|-----------|

| Length(L)          | 3.50      | ±0.10     |

| Width(W)           | 2.65      | ±0.10     |

| Height(H)          | 0.98      | ±0.10     |

| Acoustic Port (AP) | Ø0.325    | ±0.05     |

| Pin# | Pin Name | Description                                                        |

|------|----------|--------------------------------------------------------------------|

| 1    | DATA     | PDM Output                                                         |

| 2    | 2 SELECT | Lo/Hi (L/R) Select                                                 |

| 2    |          | This pin is internally pulled low but should not be left floating. |

| 3    | GND      | GND                                                                |

| 4    | CLOCK    | Clock input                                                        |

| 5    | VDD      | Power Supply                                                       |

Notes:

- Dimensions are in millimeters unless otherwise specified. •

- Tolerance is ±0.10mm unless otherwise specified. •

- Pick Area only extends to 0.25 mm of any edge or hole unless otherwise specified. •

- Suggestion to use the same date code microphone in one array microphone module. •

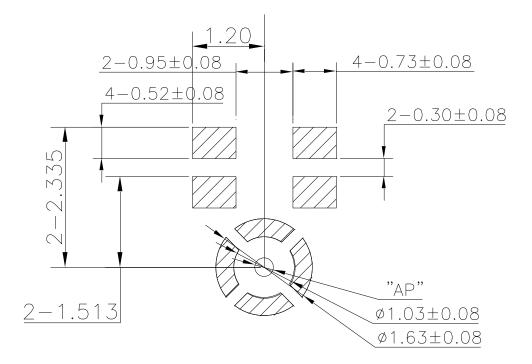

## **Example Land Pattern**

## Example Solder Stencil Pattern

Notes: Dimensions are in millimeters unless otherwise specified. Further optimizations based on application should be performed.

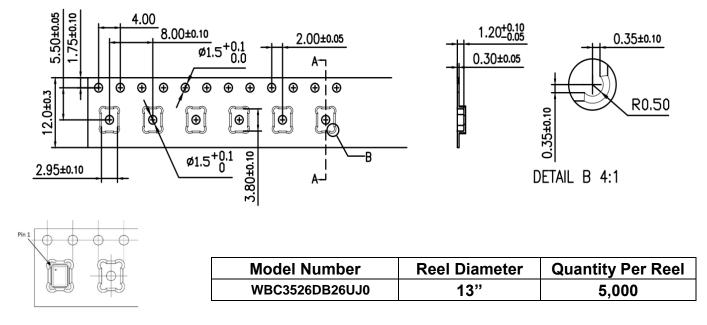

## Packaging & Marking Detail

Notes:

- Dimensions are in millimeters unless otherwise specified.

- Vacuum pickup only in the pick area indicated in Mechanical Specifications.

- Tape & reel per EIA-481.

- Labels applied directly to reel and external package.

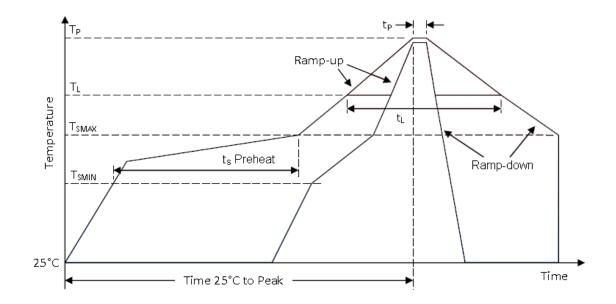

## **Referenced Reflow Profile**

| Profile Feature                                                                                   | Pb-Free                          |

|---------------------------------------------------------------------------------------------------|----------------------------------|

| Average Ramp-up rate (TSMAX to TP)                                                                | 3°C/second max.                  |

| Preheat<br>• Temperature Min (Tsmin)<br>• Temperature Max (Tsmax)<br>• Time (Tsmin to Tsmax) (ts) | 150°C<br>200°C<br>60-180 seconds |

| Time maintained above:<br>• Temperature (Τι)<br>• Time (tι)                                       | 217°C<br>60-150 seconds          |

| Peak Temperature (T <sub>P</sub> )                                                                | 260°C                            |

| Time within 5°C of actual Peak Temperature (t <sub>P</sub> )                                      | 20-40 seconds                    |

| Ramp-down rate (TP to TSMAX)                                                                      | 6°C/second max                   |

| Time 25°C to Peak Temperature                                                                     | 8 minutes max                    |

Note:

All temperatures refer to topside of the package, measured on the package body surface.

## Additional Notes

(A) Maximum of 3 reflow cycles is recommended.

- (B) In order to minimize device damage:

- Do not board wash or clean after the reflow process.

- Do not brush board with or without solvents after the reflow process.

- Do not directly expose to ultrasonic processing, welding, or cleaning.

- Do not insert any object in port hole of device at any time.

- Do not apply over 30 psi of air pressure into the port hole.

- Do not pull a vacuum over port hole of the microphone.

- Do not apply a vacuum when repacking into sealed bags at a rate faster than 0.5 atm/sec.

## **Materials Statement**

Meets the requirements of the European RoHS and Halogen-Free.

| Test                        | Description                                                                                    |

|-----------------------------|------------------------------------------------------------------------------------------------|

| Thermal Shock               | 100 cycles air-to-air thermal shock from -40°C to +125°C with 15 minute soaks.<br>(IEC 68-2-4) |

| High Temperature Storage    | 1000 hours at +105°C environment. (IEC 68-2-2 Test Ba)                                         |

| Low Temperature Storage     | 1000 hours at -40°C environment. (IEC 68-2-2 Test Aa)                                          |

| High Temperature Bias       | 1000 hours at +105°C under bias. (IEC 68-2-2 Test Ba)                                          |

| Low Temperature Bias        | 1000 hours at -40°C under bias. (IEC 68-2-2 Test Aa)                                           |

| Temperature / Humidity Bias | 1000 hours at +85°C /85% R.H. under bias. (JESD22-A101A-B)                                     |

| Vibration                   | 4 cycles of 20 to 2,000 Hz sinusoidal sweep with 20g peak acceleration lasting 12              |

|                             | minutes in X, Y, and Z directions. (Mil-Std-883E, method 2007.2 A)                             |

| ESD-HBM                     | 3 discharges of ±3.5kV direct contact to I/O pins. (ESD STM5.2)                                |

| ESD-LID/GND                 | 3 discharges of ±8 kV direct contact to lid while unit is grounded. (IEC 61000-4-2)            |

| ESD-MM                      | 3 discharges of ±200V direct contact to I/O pins. (ESD STM5.2)                                 |

| Reflow                      | 5 reflow cycles with peak temperature of +260°C.                                               |

| Mechanical Shock            | 3 pulses of 10000g in the X, Y, and Z direction. (IEC 68-2-27, Test Ea)                        |

| Drop Tost                   | To be no interference in operation after dropped to marble or 1.0cm steel plate                |

| Drop Test                   | 18 times from 1.5 meter height.                                                                |

## **Reliability Specifications**

Note:

After reliability tests are performed, the sensitivity of the microphones shall not deviate more than 3 dB from its initial value. (The measurement to be done after 2 hours of conditioning at 20 $\pm$ 2 °C, R.H 60% $\sim$ 70%)